Difference between revisions of "Tutorials:Cadence:UsingLibraryManager"

| (5 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

= Opening and Using the Library Manager = | = Opening and Using the Library Manager = | ||

| − | One of the simpler ways to navigate through the libraries ( | + | One of the simpler ways to navigate through the libraries (both the Cadence defaults, and your own custom ones) is to use the Library Manager. A library is a collection of cells, such as NOT, AND, NAND, etc. By the end of the semester, you should have full representations of most primitive gates and few complex cells. These cells contain several views, including ''schematic'', ''layout'', ''extracted'', ''symbol'', etc. |

| − | Some added conventions that will be used are as | + | Some added conventions that will be used are as follows: |

| − | Click '''CIW:Tools → Library Manager''' | + | Click '''CIW: Tools → Library Manager''' - This means the following: go to the '''CIW''' window, left-click once on the '''Tools''' menu, then left-click once on the '''Library Manager''' option in the pop-up menu that will appear. |

| − | Let's get started...click '''CIW:Tools → Library | + | Let's get started...click '''CIW: Tools → Library Manager'''. |

| − | Note: | + | '''Note:''' |

Sometimes, the window you are working in isn't big enough to display everything inside of it. When this happens, scroll-bars appear at the bottom, or the sides to allow you to see all of it. | Sometimes, the window you are working in isn't big enough to display everything inside of it. When this happens, scroll-bars appear at the bottom, or the sides to allow you to see all of it. | ||

| − | On the other hand, you may also change the size of | + | On the other hand, you may also change the size of the window. There are several ways to do this, depending on which best suits your needs. If you double click (left) on the title bar, the window will "explode" to fill your screen vertically, but it won't get any wider. Double click the menu bar (again) will return it to its original size. |

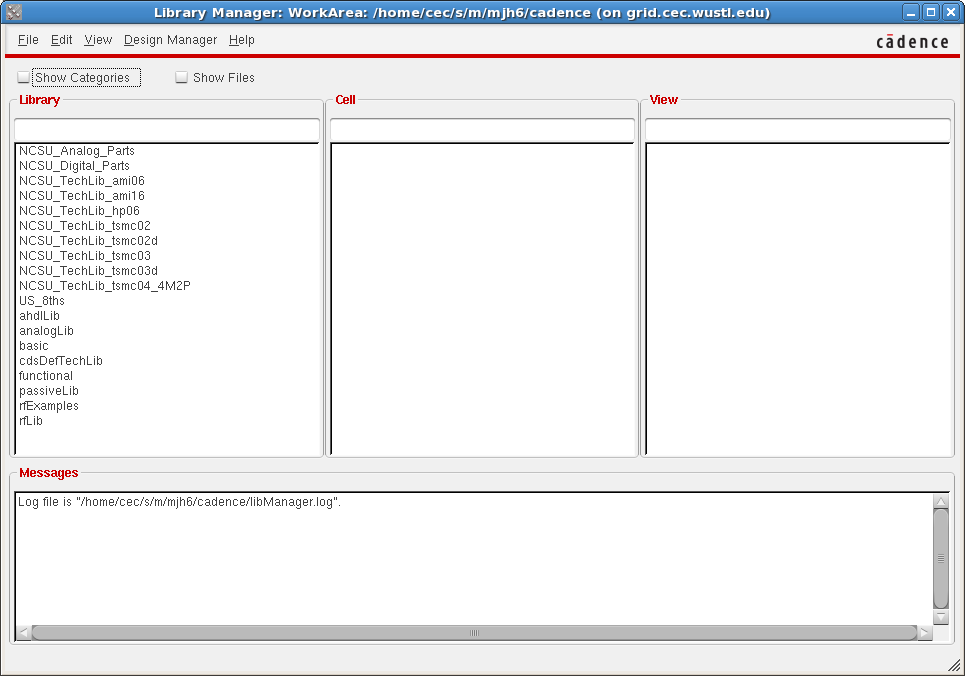

The Library Manager window should appear in just a few moments. This window should be similar to the one below: | The Library Manager window should appear in just a few moments. This window should be similar to the one below: | ||

| − | : [[File:Tutorials-Cadence- | + | : [[File:Tutorials-Cadence-UsingLibraryManager-001.png]] |

| − | The left column is a list of the current libraries. From these libraries | + | The left column is a list of the current libraries. From these libraries '''NCSU_Analog_Parts''' is of most importance. This library contains all the components used during VLSI circuit design and it will be used the most. |

| − | Left click on '''NCSU_Analog_Parts''' in the library | + | Left click on '''NCSU_Analog_Parts''' in the library browser. Left click on '''nmos4''' to display the cell views of the nmos transistor design. You should be able to see several different cell views. The cell views contain the following information: |

| − | ''symbol'' | + | {| class="wikitable" |

| − | + | ! Cell view !! Description | |

| − | ''CdsSpice, Spectre, spectreS'' | + | |- |

| − | Feel free to look at any of the cell views. To do this, click center and hold on the cell view and choose read or you can double click on the particular cell view of | + | | ''symbol'' || Contains the symbol representation of the schematic. |

| − | + | |- | |

| − | ''abstract'' | + | | ''CdsSpice, Spectre, spectreS'' || Contain spice information for the element. Feel free to look at any of the cell views. To do this, click center and hold on the cell view and choose read or you can double click on the particular cell view of interest. A window will open showing the contents of that particular window. In different cells, you may encounter the following cell views: |

| − | + | |- | |

| − | ''extracted'' | + | | ''abstract'' || Contains an abstract representation of the layout for use by Cadence place and route software. |

| − | + | |- | |

| − | ''layout'' | + | | ''extracted'' || Contains layout connectivity for use by verification programs. |

| − | + | |- | |

| − | ''schematic'' | + | | ''layout'' || Contains the silicon-level representations of the transistors and wiring (you'll do this a lot!). |

| − | + | |- | |

| − | ''behavioral'' | + | | ''schematic'' || Contains the logical design of the device. |

| − | + | |- | |

| − | + | | ''behavioral'' || Contains the VHDL description of the cell. | |

| − | [[Tutorials:Cadence: | + | |} |

| + | <noinclude> | ||

| + | [[Tutorials:Cadence:AccessingCadenceRemotely|Prev]] : [[Tutorials:Cadence:DesignHierarchy|Next]] : [[Tutorials:Cadence:Main|Up]] | ||

---- | ---- | ||

{{Template:CadenceDisclaimer}} | {{Template:CadenceDisclaimer}} | ||

| + | </noinclude> | ||

Latest revision as of 01:59, 12 November 2010

Opening and Using the Library Manager

One of the simpler ways to navigate through the libraries (both the Cadence defaults, and your own custom ones) is to use the Library Manager. A library is a collection of cells, such as NOT, AND, NAND, etc. By the end of the semester, you should have full representations of most primitive gates and few complex cells. These cells contain several views, including schematic, layout, extracted, symbol, etc.

Some added conventions that will be used are as follows:

Click CIW: Tools → Library Manager - This means the following: go to the CIW window, left-click once on the Tools menu, then left-click once on the Library Manager option in the pop-up menu that will appear.

Let's get started...click CIW: Tools → Library Manager.

Note:

Sometimes, the window you are working in isn't big enough to display everything inside of it. When this happens, scroll-bars appear at the bottom, or the sides to allow you to see all of it.

On the other hand, you may also change the size of the window. There are several ways to do this, depending on which best suits your needs. If you double click (left) on the title bar, the window will "explode" to fill your screen vertically, but it won't get any wider. Double click the menu bar (again) will return it to its original size.

The Library Manager window should appear in just a few moments. This window should be similar to the one below:

The left column is a list of the current libraries. From these libraries NCSU_Analog_Parts is of most importance. This library contains all the components used during VLSI circuit design and it will be used the most.

Left click on NCSU_Analog_Parts in the library browser. Left click on nmos4 to display the cell views of the nmos transistor design. You should be able to see several different cell views. The cell views contain the following information:

| Cell view | Description |

|---|---|

| symbol | Contains the symbol representation of the schematic. |

| CdsSpice, Spectre, spectreS | Contain spice information for the element. Feel free to look at any of the cell views. To do this, click center and hold on the cell view and choose read or you can double click on the particular cell view of interest. A window will open showing the contents of that particular window. In different cells, you may encounter the following cell views: |

| abstract | Contains an abstract representation of the layout for use by Cadence place and route software. |

| extracted | Contains layout connectivity for use by verification programs. |

| layout | Contains the silicon-level representations of the transistors and wiring (you'll do this a lot!). |

| schematic | Contains the logical design of the device. |

| behavioral | Contains the VHDL description of the cell. |

Information is provided "as is" without warranty or guarantee of any kind. No statement is made and no attempt has been made to examine the information, either with respect to operability, origin, authorship, or otherwise.

Please use this information at your own risk--and any attempt to use this information is at your own risk--we recommend using it on a copy of your data to be sure you understand what it does and under what conditions. Keep your master intact until you are personally satisfied with the use of this information within your environment."

Cadence® is a trademark of Cadence Design Systems, Inc., 555 River Oaks Parkway, San Jose, CA 95134

For web related questions contact: Viktor Gruev, Michael Hall