How to use inherited connections

Help resources

- IC-6146.14 → Virtuoso Schematic Editor → Virtuoso Schematic Editor L User Guide; → Understanding Connectivity and Naming Conventions → Inherited Connections

- IC-6146.14 → Virtuoso Layout Suite → Virtuoso Layout Suite L User Guide → Editing and Defining Properties → Using Net Expressions and Inherited Connections

Inherited connections provide a convenient way to use multiple power supplies in a design by defining a single power supply in a low-level schematic that is overridable. This can reduce the need to draw power and gnd pin connections explicitly on each symbol (useful for digital gates). In this how-to, a method for using and defining inherited connections will be given.

Note, the NCSU Design Toolkit replaces the basic library from Cadence with its own which may not have the vdd_inherit or gnd_inherit cells. To add this library to your CDS project with the name basic_cds, add the following line to the cds.lib file:

DEFINE basic_cds $IC/tools/dfII/etc/cdslib/basic

Inherited connections use Net Expressions in Cadence which provide a way of renaming a net. There are four components of a net expression (ex. [@search property name:%:default global search name]):

- search scope

- search property name

- format instruction

- default global search name - shows what the wire or pin is connected to by default

When a net expression is formed, an asterisk (*) is shown after the global name indicating that it is a net expression.

In the basic_cds library, there are four inherited supply symbols. These are given in the table below along with their associated net exprssion label:

| Inherited Supply Symbol | Net Expression Label |

|---|---|

vcc_inherit |

[@vcc:%:vcc!]

|

vdd_inherit |

[@vdd:%:vdd!]

|

gnd_inherit |

[@gnd:%:gnd!]

|

vss_inherit |

[@vss:%:vss!]

|

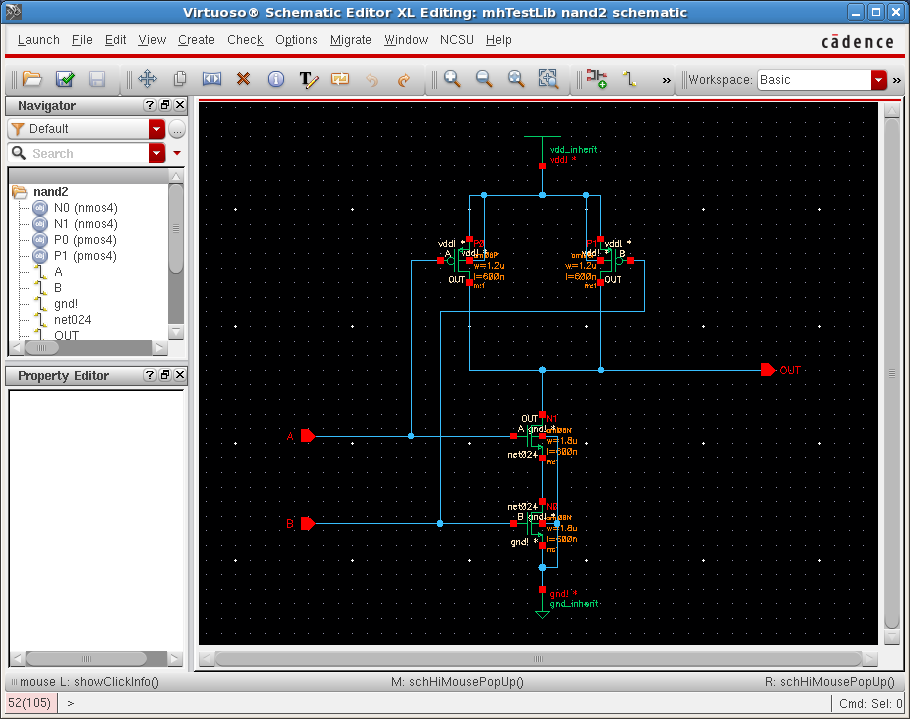

nand2 gate

Here, is an example of using inherited connections using a 2-input NAND gate (nand2).

First, in the Library Manager, create a new schematic cell view using File → New → Cell View.... Then under the field Cell, type nand2. For Type select schematic. And for the View type schematic. Then draw the nand2 gate as shown below using the vdd_inherit and gnd_inherit symbols from the basic_cds library.

Next, create a test schematic for the nand2 gate called nand2_test. This test schematic is designed to override the power supply nets by using Net Expressions. The overrides are shown in yellow on the schematic. The global vdd! net is set to 5V and the vdd power supply of the nand2 gate is set to 3.3V!:

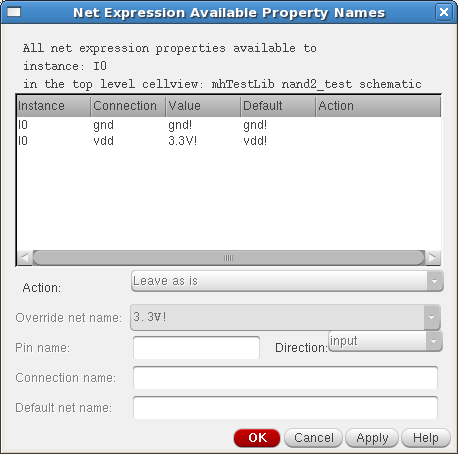

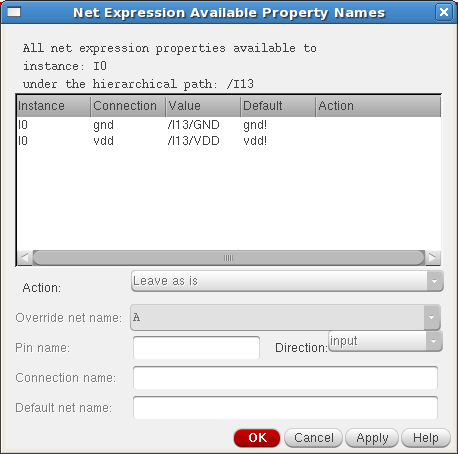

The Net Expressions can be set by Edit → Net Expressions → Available Properties.... This brings up the window below. The net expressions will be shown for the currently selected components. Select the nand2 component to show its Net Expressions.

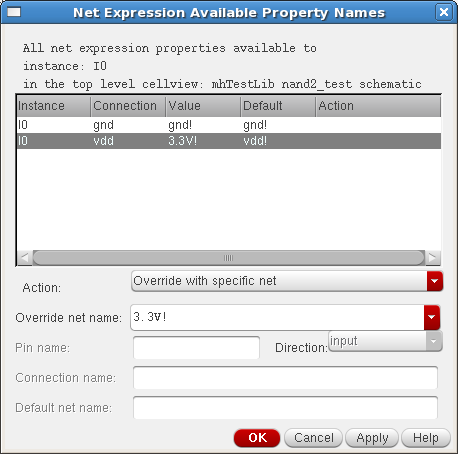

Select the vdd connection. Under Action, select Overrride with specific net. Type the net name 3.3V!. This now corresponds to the 3.3V! net defined in the test schematic.

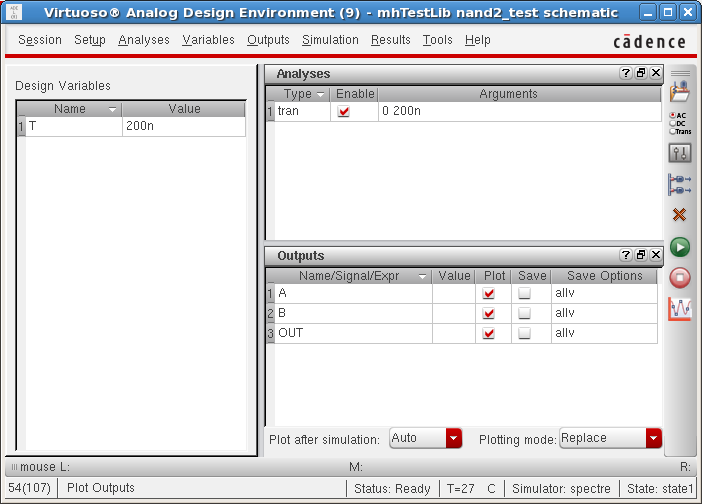

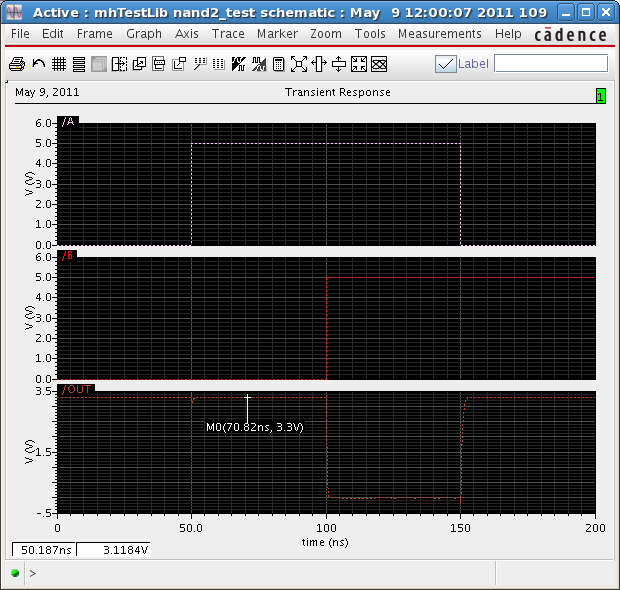

Next, a simulation is done to show that the power supply of the output from the nand2 gate is at 3.3V and not 5V. The simulation setup is shown below:

The simulations results here show that the OUT net swings from 0V to 3.3V.

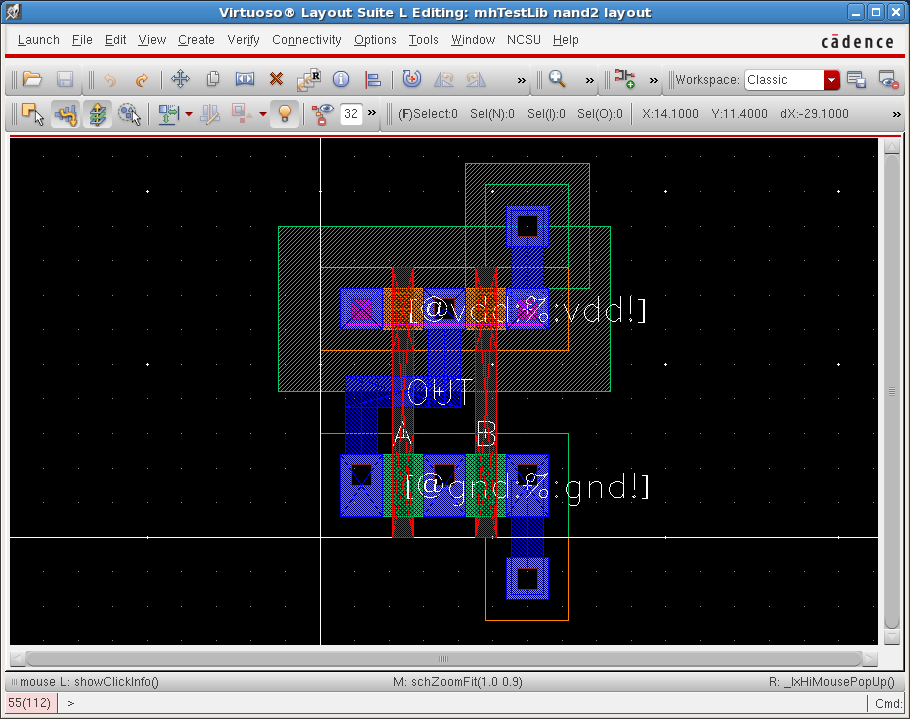

Then, a layout of the nand2 gate is constructed. The pins on this layout are defined using Net Expressions:

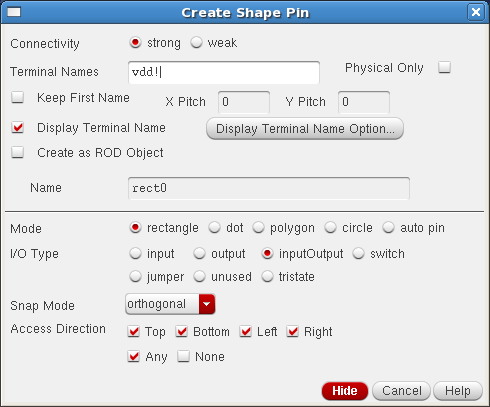

When creating a pin for an inherited power supply (such as vdd_inherit), define the terminal name using the default global search name. In the case of the vdd inherited connection, this would be vdd!:

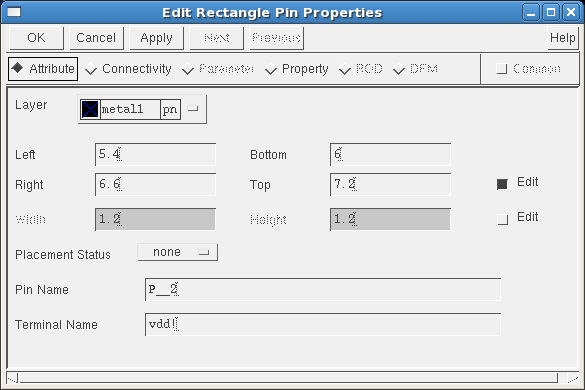

After placing the pin in the layout, select it and open up the properties (Edit → Basic → Properties... or bind key q). This shows the terminal name is vdd! under the Attribute tab as was defined earlier.

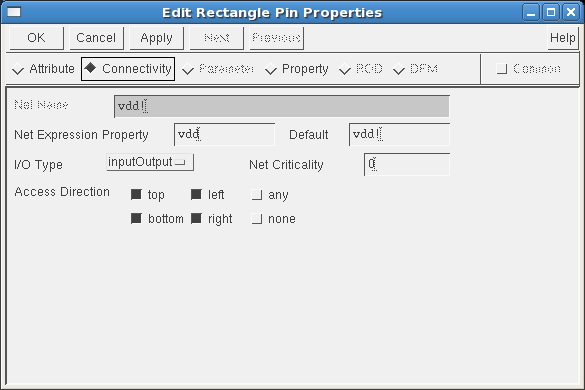

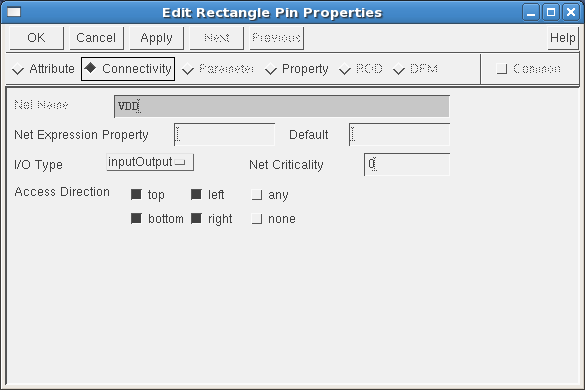

Then click on the Connectivity tab. Here, Net Expressions can be defined on the pin. Under Net Expression Property, type vdd for the inherited net name, and under Default, type vdd! for the default global search name.

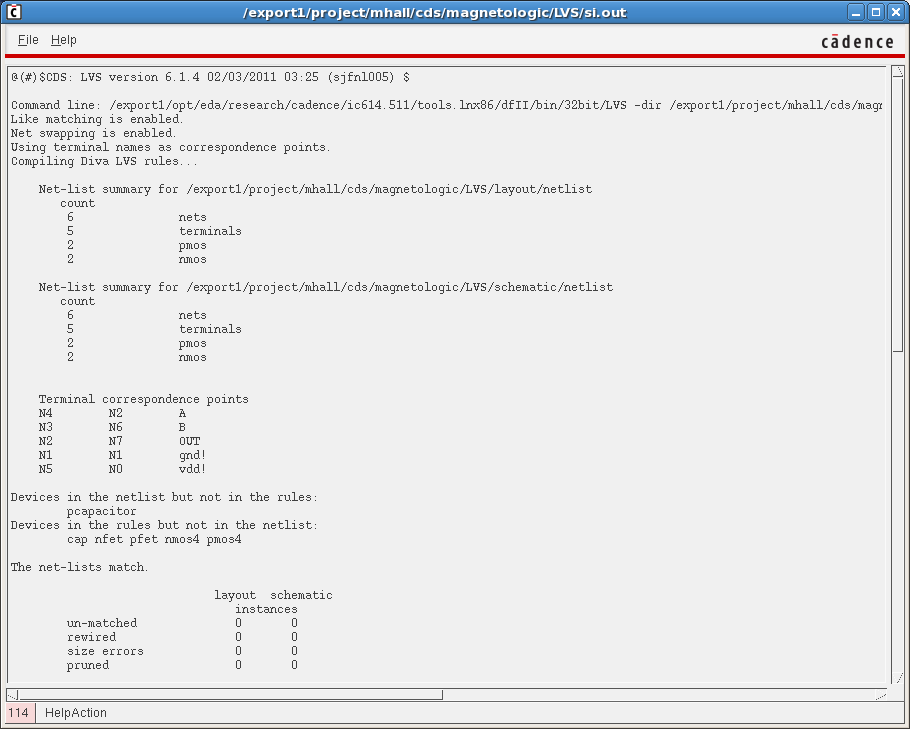

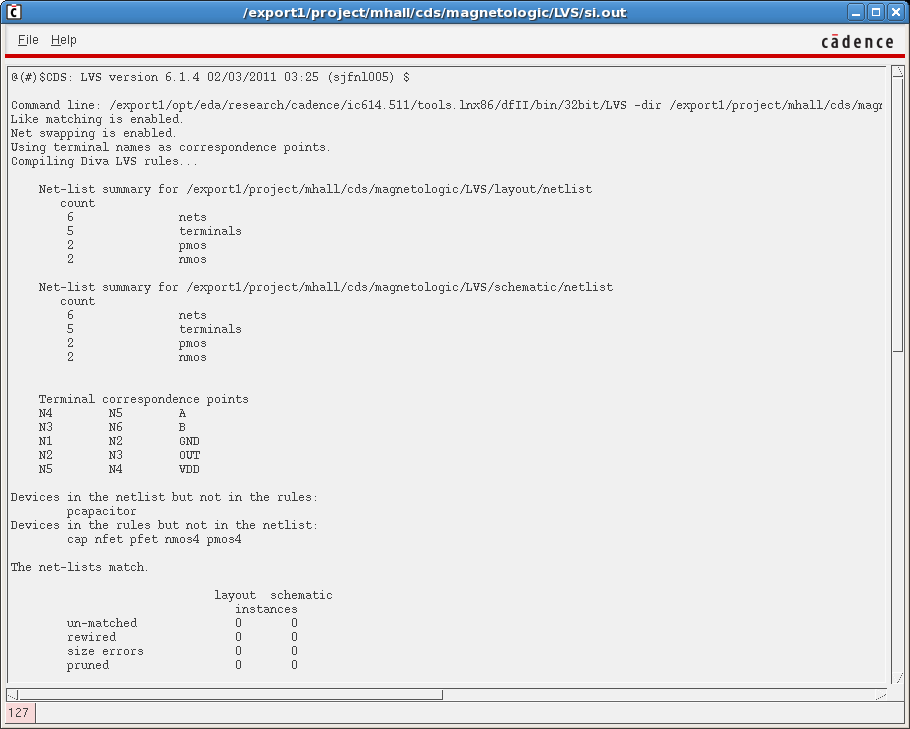

Next, a DRC check is performed on the layout, followed by an extraction of the layout. Then the LVS tool is brought up as shown below to compare between the extracted view and schematic:

The results of the LVS check show that everything matches between the layout and the schematic:

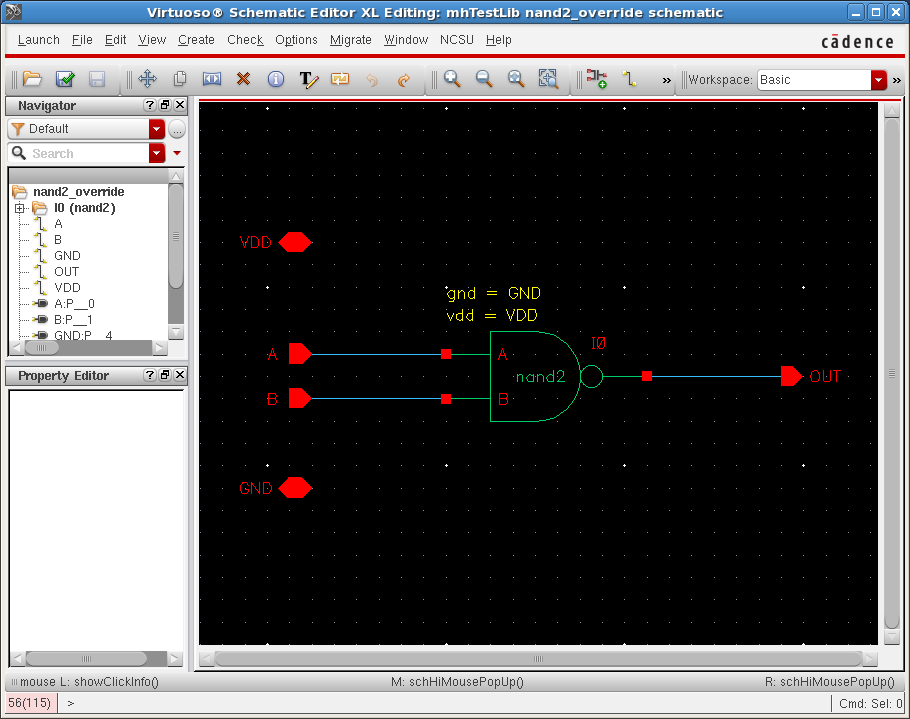

Next, a new cell is created called nand2_override. This cell is designed to override the power and gnd supplies and route them to explicit pins. The schematic is drawn below:

Net Expressions are set on the nand2 gate to connect the gnd and vdd connections to the GND and VDD pins:

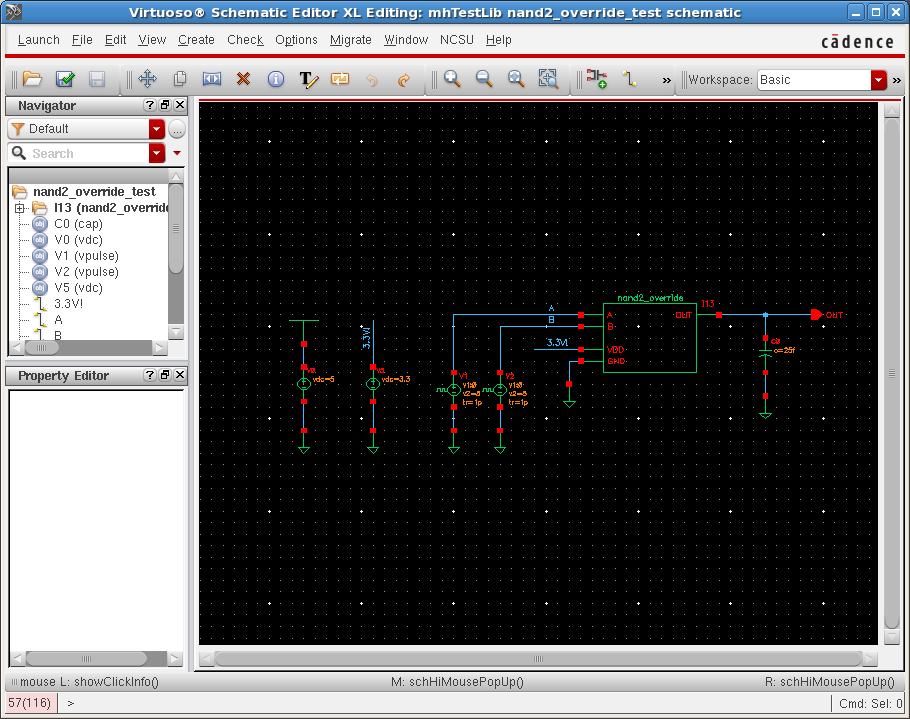

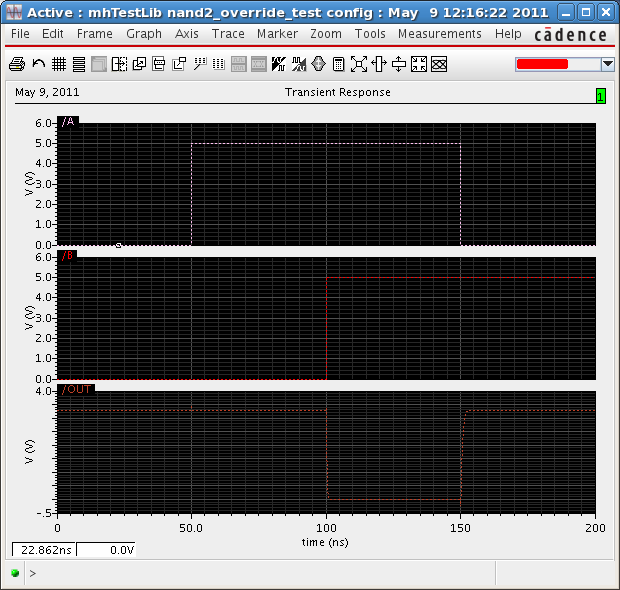

Then, a test schematic is drawn for the nand2_override cell called nand2_override_test. In this test schematic, the VDD input pin is set to the 3.3V! net.

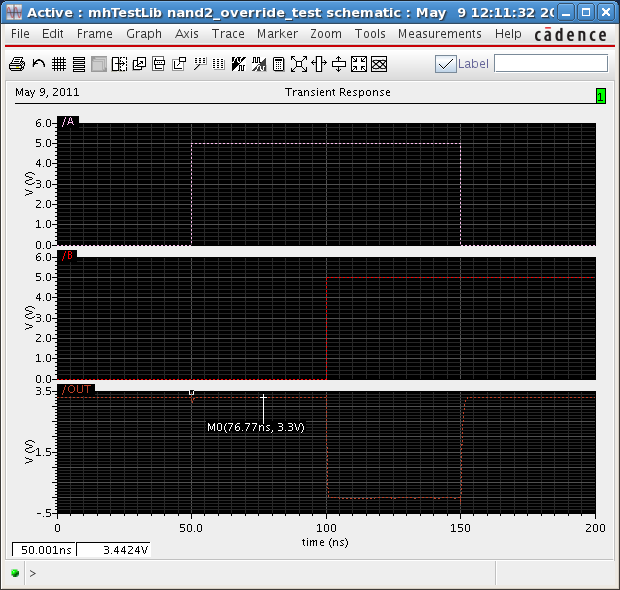

The simulation results on this test schematic show that the OUT net swings between 0V and 3.3V.

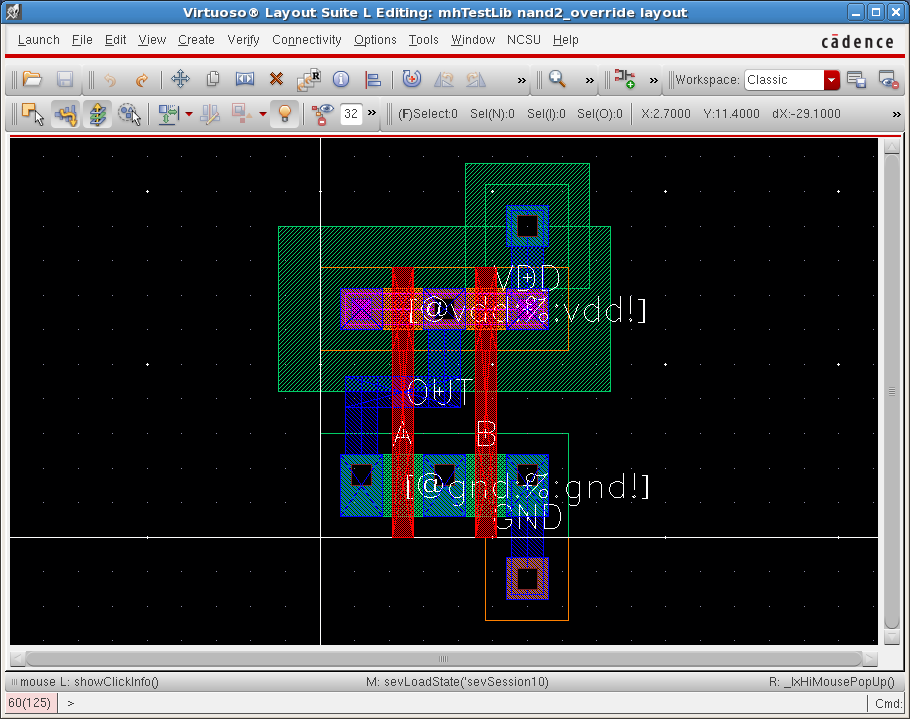

The layout for the nand2_override cell is then drawn as shown below. It is the same layout as the nand2 cell, but the pins are redefined to be VDD and GND as shown below.

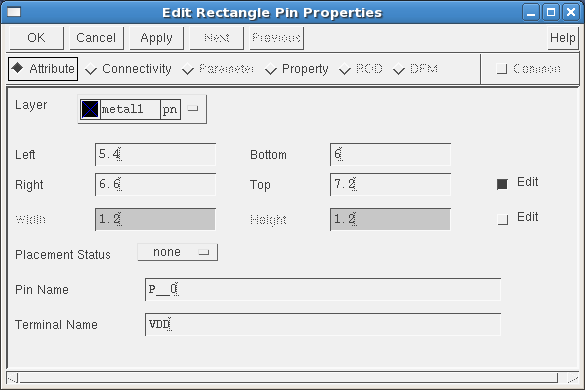

Here is the pin properties for the VDD pin:

Under the Connectivity tab, there is no net expression defined as it is unnecessary.

The LVS tool then is used to compare the layout and schematic view:

The results of the LVS check show that the layout and schematic views match.

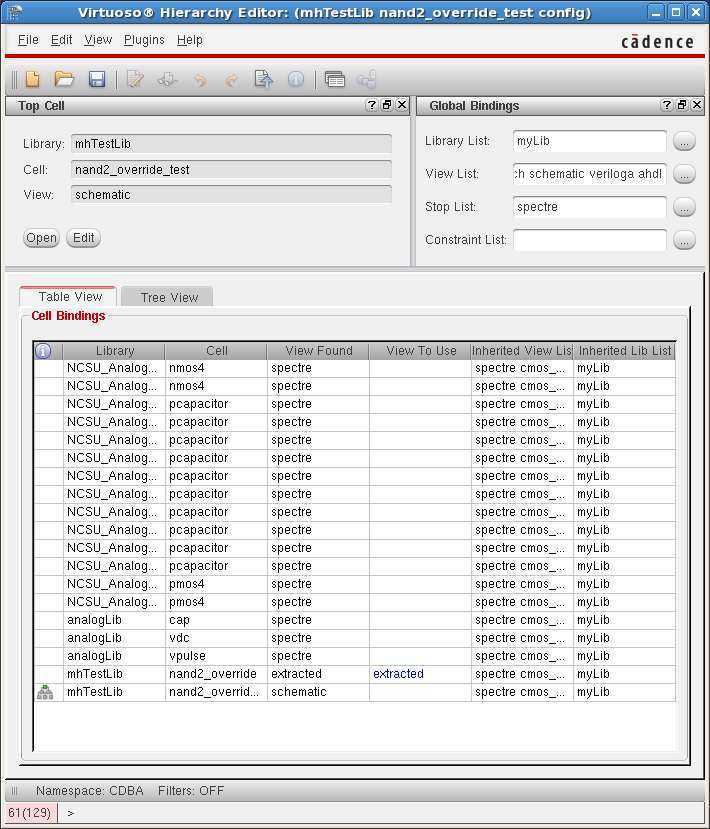

The extracted view of this cell can be used in simulation by creating a config view of the nand2_override_test schematic. The config view is shown below. In this case, the nand2_override cell view in the Cell Bindings is set to use the extracted view.

Simulations using the config view show that the output swings between 0V and 3.3V.